URL: https://fe.desy.de/fec/projects/high_energy_physics/tangerine/@@siteview

Breadcrumb Navigation

Tangerine

Project Goal:Validation and performance study of a 65-nm CIS process for future applications in particle physics, astro-particle physics and photon science Partners:

Project Status:Running

|

|

|

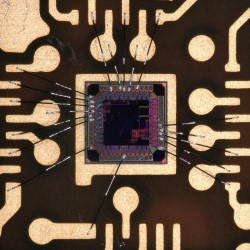

The project Tangerine (Towards Next Generation Silicon Detectors) is intended to exploit the features of new CMOS imaging processes suitable for monolithic active pixel detectors (MAPS) with a smaller CMOS node. MAPS integrate both the sensor and the readout circuitry into the same piece of silicon, where this project utilizes a 65-nm quadruple well process from TPSCo. They come along with a significant reduction of the material budget, due to the absence of a separate readout chip and possible substrate thinning down to the sensing epitaxial layer. Furthermore, DESY is partner of a parallel running project called H2M (Hybrid-to-Monolithic), led by CERN. We design the full pixel front-end circuitry consisting of an amplifier with Krummenacher feedback and comparator in the same CIS technology. |

|