URL: https://fe.desy.de/fea/projects/petraiii_daq_system/petraiii_daq_board/@@siteview

Breadcrumb Navigation

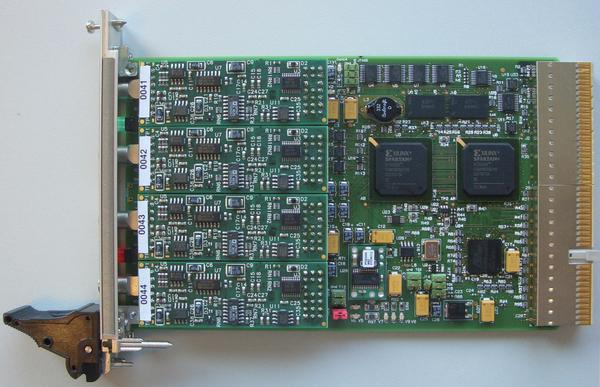

PETRAIII Readout Board

This readout card works like a Transient Recorder and collects data from the ADC Mezzanine Boards, calculates trigger event, stores data in a ring buffer and transmits this data to the host computer via PCI bus, after receiving an external main trigger signal.

The ADC Mezzanine Boards provide high accuracy and low noise acquisition. All channels operate in parallel. The Transient Recorder is FPGA-based, 3U PXI module and can be used in either PXI or CompactPCI systems.

It is designed for PETRA-III ELWIS control system.

The Transient Recorder includes the following main parts:

- 2 FPGA - SPARTAN-3XILINX,

- SDRAM memory for ring buffer – 512 Mb

- PCI Bridge – PCI9030

- 4 ADC Mezzanine Boards

Main Features

- Form factor: 3HE PXI

- 4x ADC 14 bit / 10 MHz Mezzanine Boards

- Mezzanine Boards exchangeable for with Board with other functions (example DAC)

- External Clock Source (PXI) or Internal (FPGA)

- Universal External Trigger Sources (PXI-Trigger Bus), all lines usable

- Internal Trigger Source

- User defined Trigger Algorithm

- Full user reprogrammable FPGA’s

- 64MByte SDRAM

- Chip with unique Serial Number and temperature measurement