URL: https://fe.desy.de/fea/projects/10g_developments/readout_board_for_pixel_detectors/@@siteview

Breadcrumb Navigation

Digital Readout Board for Pixel Detectors

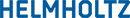

Top Side of the Readout Module. On the left side are the 4 10G Ethernet channels with PHYs and SFP+ Connectors, On bottom is the CF Card slot and on the right side the Virtex5 FPGA

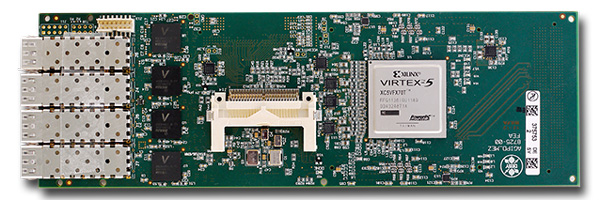

Bottom Side of Readout module. On the right side is the I/O connector located, which will typically used as digital reaout interface to a pixel detector. left to it are the 2 SODIMM slots for DDR2 memory. On the bottom is the connector for supply voltages and control.

Description

This FPGA-based mezzanine card has been designed for fast digital readout of Pixel Detectors. It holds all the necessary infrastructure for data acquisition applications in the range of up to 100 GBit/s. Digital signals are being read via up to 146 LVDS pairs operating at maximum data rate of 800 MBit/s each. The preprocessed data is being strreamed via 4 10 GBit Ethernet links to standard computing hardware.

Key Features

FPGA

- XILINX XC5VFX70T-1FFG1136

- 16 Gigabit Transceivers (RocketIO)

- 640 User I/Os

- Built in PowerPC for Control applications

Memory

- 2 x DDR2 SO-DIMM up to 2 x 4 GByte

- 68 GBit/s bandwidth up to 80 GBit/s possible depending on FPGA speed grade

Configuration

- Onboard configuration circuitry (JTAG)

- 2 x 32MB Platform Flash

- System ACE with Compact FLASH

- Dynamic Reconfiguration: From/To external Mezzanine card

Communications and Networking

- 4 x SFP(+) 10GE, 1GE transceiver connectors

- serial buses (RS232, SPI, I2C)

- parallel µController bus

The mezzanine card will be utilized at AGIPD, LAMDA and PERCIVAL.