URL: https://fe.desy.de/sites/site_fe/content/fec/projects/@@siteview

Breadcrumb Navigation

Projects

FEC is involved in the following projects:

|

|

|

|

Project Goal: |

|

|

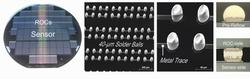

With the LHC going beyond its initial design performance, the current barrel pixel detector of the CMS experiment at CERN will reach its performance limits and suffer more and more from radiation damage. Therefore, it is planned to install a new detector with better performance, to which DESY and the University of Hamburg will contribute. We build up one half-shell of the outermost layer, consisting of 256 modules with 17 million pixels in total. The central part of the FEC contribution is the production of silicon-bare modules for the outermost layer using bump bonding interconnection techniques. |

|

|

|

|

|

Partners: |

|

|

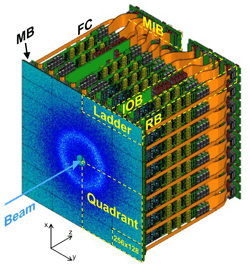

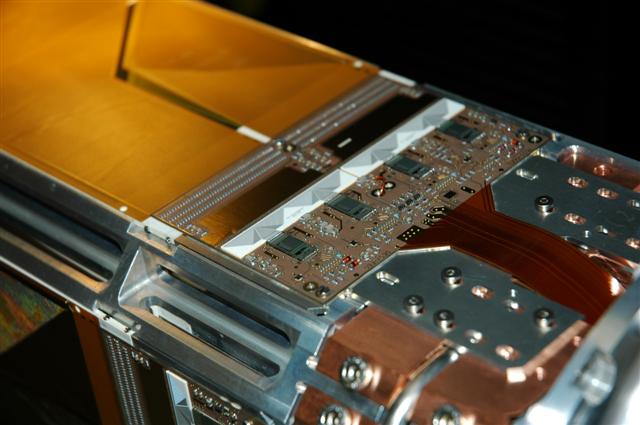

The European X-ray Free Electron Laser (XFEL) facility will provide uniquely intense and coherent short-pulse radiation in the X-ray regime. Up to 3000 pulses will be delivered with a minimal temporal spacing of ?200 ns between each pulse and an overall repetition rate of 10 Hz. In order to utilize the fast 200-ns pulse separation and to investigate dynamics on that time scale at experiments, the development of a new area detector called DEPFET Sensor with Signal Compression (DSSC) has been started in 2009. The DSSC X-ray imager is a mega-pixel camera combining a single-photon resolution capability at low photon numbers of up to 14 photons with a wide dynamic range of up to 6,000 1-keV photons and a frame-rate capability of up to 5 MHz. DESY-FEC is involved in the development of the focal-plane electronics, comprizing the design of the ASICs for the readout of the DEPFET arrays as well as of the hybrid modules. |

|

|

|

|

|

(HASYLAB) |

|

|

Partners: |

|

|

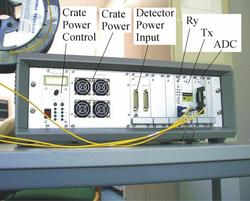

The PXI-based DAQ system is collecting and measuring electrical signals from the SDD and transducers and putting them to a computer for histograming and to safety circuits for user-friendly and safe usage, respectively. Furthermore, the system provides all necessary supply voltages and takes over device control. The master is formed by a versatile single-board computer for PXI-bus control with processor, on-board memory, hard disk, and PCIe Gigabit Ethernet controller for high-speed communication. An A/D converter board offers a 12-bit resolution and is operated at 1 MSps per SDD channel. An user-specific gate signal can be used for beamline-controlled data taking. The SDD module's ambient temperature, humidity and pressure are also monitored. |

|

|

|

||

|

(HASYLAB) |

||

|

Project Goal: |

||

|

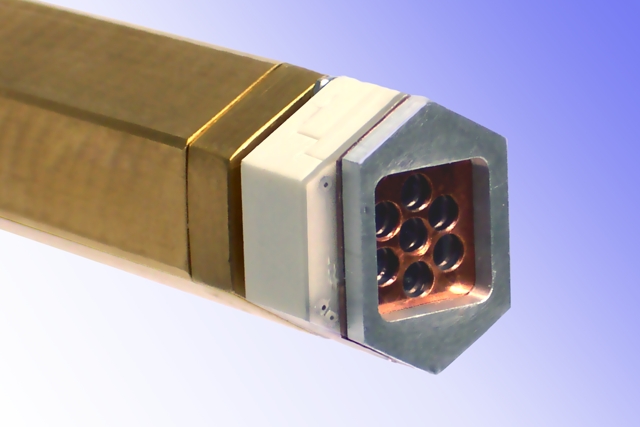

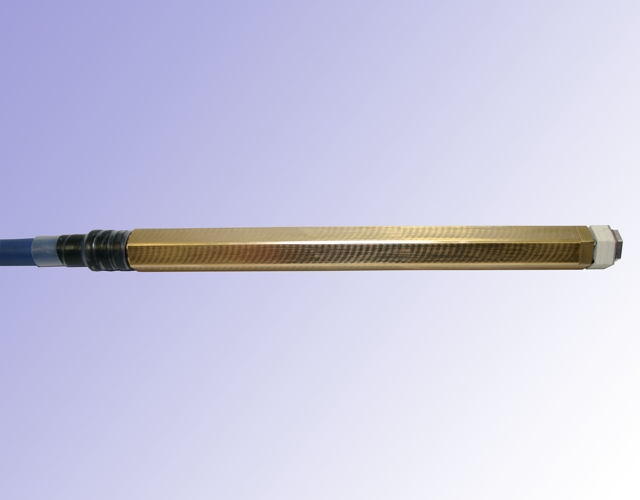

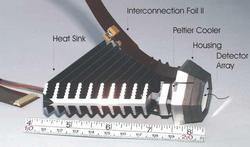

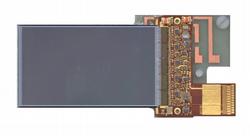

The Peltier-cooled 7-cell SDD module comprises a sensor with 7 x 7-mm² active area, an ASIC for amplification, shaping and detection, storage, and derandomized readout of signal pulses in parallel, and amplifiers for line driving. The compactness and hexagonal shape of the module with a wrench size of 16 mm allow very short distances to the specimen and flexible multi-module arrangements. The overall power dissipation is 186mW. At a shaper peaking time of 190ns and an integration time of 450ns an electronic rms noise of ~11 electrons was achieved. When operated at 7°C, FWHM line widths around 260eV and 460eV (Cu-Kα) were obtained at low rates and at sum-count rates of 1.7MHz, respectively. The peak shift is below 1% for a broad range of count rates. At 1.7-MHz sum-count rate the throughput loss amounts to 30%. The module is already in use at synchrotron beamlines for fast X-ray spectroscopy experiments like XAFS and XSW. |

||

|

|

|

|

(HASYLAB, supported by the European Commission) |

|

|

Project Goal: |

|

|

7-ch silicon drift detector module with post amplifiers and shapers for count rates of up to 200 kcts/s/ch. The outputs are connectable to conventional peak-finding ADCs and MCAs. |

|

|

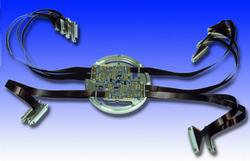

61-ch silicon drift detector-demonstrator module with an active area of 3 cm² count rates up to some hundred kcts/s/ch and an energy resolution of some hundred eV (FWHM) within 1 to 30 keV. Its hexagonal geometry with sloped sidewalls approaches the optimum spherical module arrangement. |

|

|

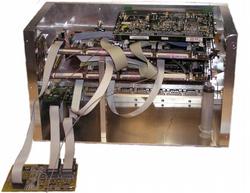

Data-acquisition system for X-ray spectroscopic and imaging applications. It has the capability to process the signals of up to 120 silicon drift detector channels in parallel. The signal processing comprises a 12-bit digitization at 1MSps per detector channel, an optical readout at 2.488Gbit/s, and an online histogramming with a counting depth of 32 bits per energy class and channel. |

|

|

The user gains full system control and VMEbus-based data access by an additional bidirectional optical link and a commercial VME controller, respectively. The modular system's setup assures an upgradability to 1860 detector channels in steps of 120. |

|

|

|

|

|

(supported in part by the European Commission DGXII under contract ERBFMGECT980104) |

|

|

Project Goal: |

|

|

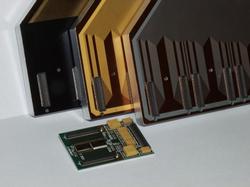

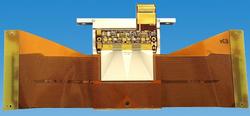

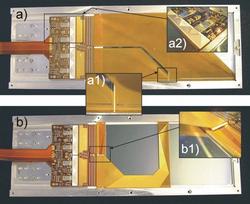

Anode structures (1280 electrodes at 150 micron pitch) in different technologies and hybrid interface circuit to be assembled with two 64-ch JAMEX readout ASICs. |

|

|

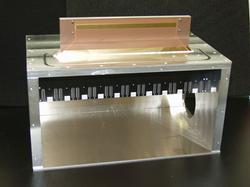

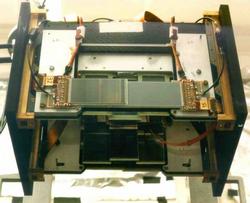

Housing of the integrating detector system with anode structure. The Data-acquisition system will be placed in the remaining volume inside the housing. |

|

|

Fully assembled integrating detector system with DAQ electronics. The system allows fast time-resolved SAXS on a sub-photon noise floor even at very high rates up to 10^12 photons/mm2/s. |

|

|

|

|

|

(DESY) |

|

|

Project Goal: |

|

|

|

|

|

(DESY) |

|

|

Project Goal: |

|

|

|

|

|

(DESY) |

|

|

Project Goal: |

|

|

|

|

|

(DESY) |

|

|

Project Goal: |

|